2010-05-17

# **STARPOWER ID- IPM**<hr/> **Application Note**

1

# Table of Contents

# Chapter 1 Starpower IPM Product Outlines

- 1.1 Introduction

- 1.2 Starpower IPM Outlines and Line-up

- 1.2.1 Drawing

- 1.2.2 Marking

- 1.2.3 Home appliances & Industrial application

# 1.3 Internal Circuit and Features

- 1.3.1 Internal Block Diagram

- 1.3.2 Features and Functions

# Chapter 2 Electrical Characteristics

# 2.1 Description of the input and output pins

- 2.1.1 Input / Output Port Description

- 2.1.2 Pin Definition Explanation

- 2.1.3 Driving and Protection Functions

- 2.2 Static Characteristics

- 2.3 Dynamic Characteristics

# Chapter 3 Packaging and Installation Guide

- 3.1 Package

- 3.2 Installation Guide

- 3.2.1 Heat Sink Mounting

- 3.2.2 Screw Tightening Torque

- 3.3 Handling Precaution and Storage Notices

- 3.4 Marking specification

# Chapter 4 Applications Description

- 4.1 System Connection Diagram

- 4.2 Structure of Signal Input Terminals

# 4.3 Bootstrap Circuit

- 4.3.1 Operation of a Bootstrap Circuit

- 4.3.2 Initial Charging of a Bootstrap Capacitor

- 4.3.3 Bootstrap Capacitor Selecting

- 4.3.4 Series Resistor Selecting

- 4.3.5 Bootstrap Diode Selecting

# 4.4 Application Circuit and Recommended Parts

- 4.4.1 Direct Input (without Opto-Coupler) Interface Example

- 4.4.2 Interface Example When a Opto-Coupler is Used

# 4.5 Input / Output Timing Diagram

# 4.6 Function and Protection Timing Charts

- 4.6.1 Timing Charts of Short Circuit Protection

- 4.6.2 Timing Charts of Under-Voltage Protection

- 4.6.3 Fault Output Loop

- 4.6.4 Selecting the Current Sensing Shunt Resistor Value

- 4.6.5 Filter Circuit Setting (RC Time Constant) for Short-Circuit Operation

- 4.6.6 Parallel Connection

- 4.6.7 Trouble Shooting of IPM

# Chapter 5 Safe Operating Area

# 5.1 Safe operating area of the IPM

- 5.1.1 Definition of SOA

- 5.1.2 Switching Operation

- 5.2 Noise Immunity Capability

- 5.3 ESD Withstand Capability

# Chapter 6 Reference Design

- 6.1 Demo Board Introduction

- 6.2 Layout Guide-line

# Chapter 7 Thermal Resistances Concept and Introduction

- 7.1 Overview

- 7.2 Measurement Method

- 7.3 Measurement Procedures

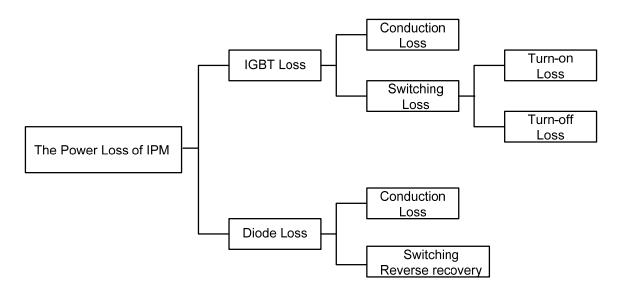

# Chapter 8 Power Loss and Dissipation

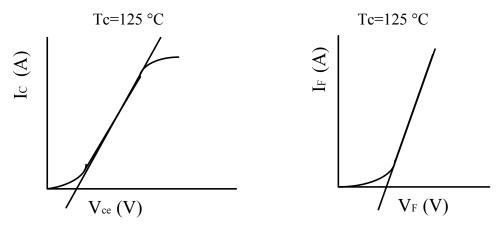

- 8.1 Conduction Loss and calculation Method

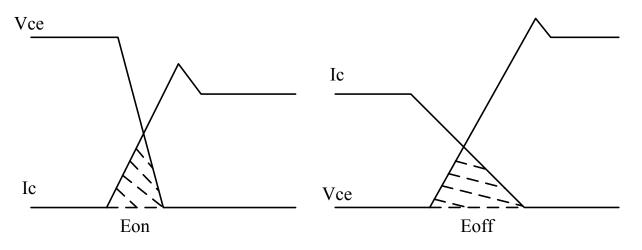

- 8.2 Switching Loss and calculation Method

# Chapter 9 Appendix Document

- 9.1 F.A.Q for Starpower ID IPM

- 9.2 Divided negative dc-link terminals for current sensing applications

- 9.3 IPM Selection example

# Chapter 10 Contact Information

# Chapter 1 Starpower IPM Product Outlines

# 1.1 Introductions

Inverter technology brings obviously advantages like: energy efficient and quiet-running compare to the conventional motor drives technology. With the advantages of compactness, built-in control, and lower overall-cost modules requirements are increasing for low-power motor control applications. Starpower's ID series IPM is provided with compact, high-functionality, and high efficiency to meet these needs.

ID series IPM is an attractive choice which alternative to conventional discrete solution for low-power motor drives, specifically for appliances such as air conditioning, washing machines. ID series IPM combines optimized driver and protection circuit which matched to the IGBT's switching characteristics. ID series IPM is also provided with highly effective short-circuit detection and protection functions through the use of real time current sensing technique together with under-voltage protection function to prevent over heat condition when driving voltage is not working normally.

This application note shows the details of ID series IPM. The designer could easily understand and learn how to adopt the parts to his system design by aid of the quick study of the application note.

# 1.2 Starpower ID-IPM Outlines and Series

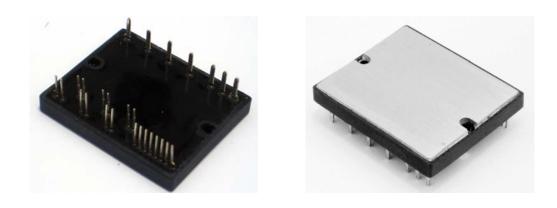

Figure 1-1. Outline of ID-IPM (ID20FT06A1S)

4

16 VS(U)

18 VCC

17 IN(WH)

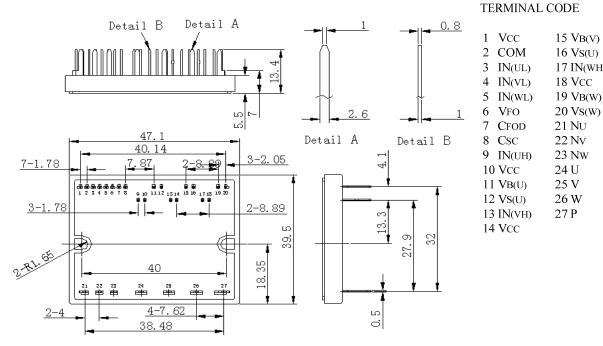

### 1.2.1 Drawing

Figure 1-2. Package Outlines

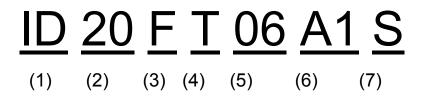

### 1.2.2 **Ordering Information**

- (1) Device: Intelligent Power Module

- (2) Current Rating: 20=20A

- (3) Circuit Configuration: F=Three Phase, P=Seven Pack

- (4) Chip Characteristics: L=NPT Low Loss, T=Trench Low Loss

- (5) Voltage Rating: 06=600V, 12=1200V

- (6) Package Style

- (7) Options

### 1.2.3 **Starpower ID-IPM Series**

Table 1-1. Starpower ID-IPM Series and General Applications

5

| Part Number | Ratings  | Motor Ratings(*) | PWM<br>Frequency(Typ.) | Remark                                     |

|-------------|----------|------------------|------------------------|--------------------------------------------|

| ID10FT06A1S | 600V/10A | 0.5 KW/220Vac    | 15kHz                  |                                            |

| ID15FT06A1S | 600V/15A | 0.75 KW/220Vac   | 15kHz                  | V <sub>iso</sub> = AC 2500V <sub>rms</sub> |

| ID20FT06A1S | 600V/20A | 1.5 KW/220Vac    | 15kHz                  | (Sinusoidal 1min)                          |

| ID30FT06A1S | 600V/30A | 2.2 KW/220Vac    | 15kHz                  |                                            |

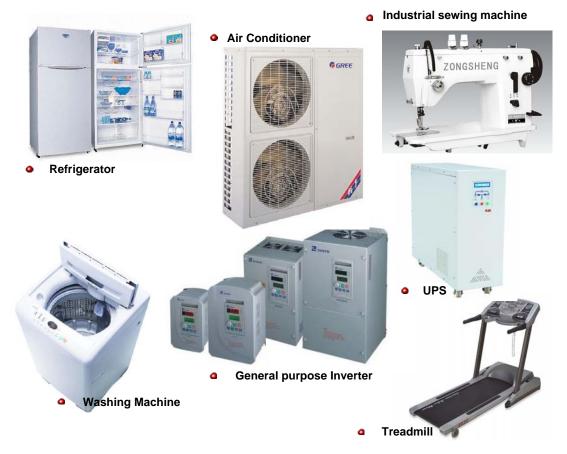

# 1.3 Home appliances & Industrial application

Motor drive for household electric appliances: air conditioners, washing machines, refrigerators, low power industrial applications such as treadmill and general purpose inverter as well. IPM is the best choice for the low power motor drivers.

Figure 1-3. Home and industrial application areas

# 1.4 Internal circuit and Features

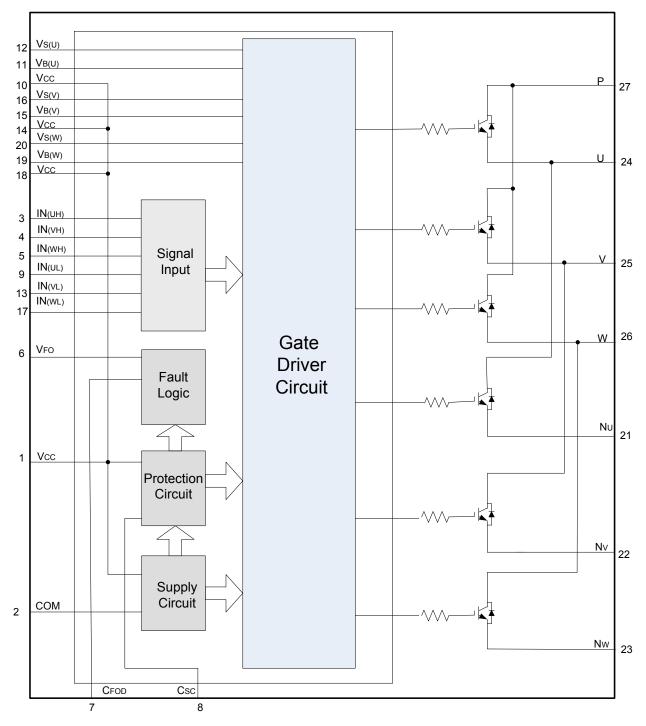

1.4.1 Internal Block Diagram

# 1.4.2 Features and Functions

# Features

- UL Certified (UL 1557).

- Low power dissipation and excellent thermal package design.

- Low temperature coefficient effect both for driver and IGBT.

- Divided negative dc-link terminals for inverter current sharing application.

- Matched propagation delay for all channels.

- Lead-Free packaging and RoHS compatible.

- Provided a fault signal (V<sub>FO</sub> pin) and shut-off internal IGBT when OC/SC and under-voltage event occur.

# **Chapter 2** Electrical Characteristics

# 2.1 Description of the Input and Output Pins

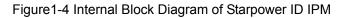

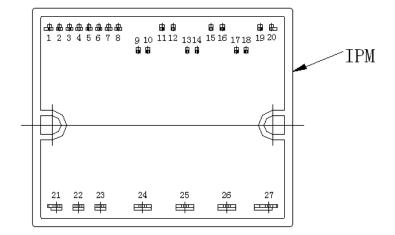

Figure 2-1. Pin Definition of ID IPM (ID20FT06A1S)

| No. | Symbol              | Pin Description                                               |

|-----|---------------------|---------------------------------------------------------------|

| 1   | V <sub>cc</sub>     | Supply Voltage Terminal for Driver IC                         |

| 2   | СОМ                 | Common Supply Ground                                          |

| 3   | IN <sub>(UL</sub> ) | Signal Input for Low-side U Phase                             |

| 4   | IN <sub>(VL)</sub>  | Signal Input for Low-side V Phase                             |

| 5   | IN <sub>(WL)</sub>  | Signal Input for Low-side W Phase                             |

| 6   | V <sub>FO</sub>     | Fault Output                                                  |

| 7   | C <sub>FOD</sub>    | Capacitor for Fault Output Duration Time Selection            |

| 8   | C <sub>SC</sub>     | Capacitor (Low-pass Filter) for Short-Current Detection Input |

| 9   | IN <sub>(UH)</sub>  | Signal Input for High-side U Phase                            |

| 10  | V <sub>CC</sub>     | Supply Voltage for Driver IC                                  |

| 11  | V <sub>B(U)</sub>   | High - side Bias Voltage for U Phase IGBT Driving             |

| 12  | V <sub>S(U)</sub>   | High - side Bias Voltage Ground for U Phase IGBT Driving      |

| 13  | IN <sub>(VH)</sub>  | Signal Input for High-side V Phase                            |

| 14  | V <sub>CC</sub>     | Supply Voltage for Driver IC                                  |

| 15  | V <sub>B(V)</sub>   | High - side Bias Voltage for V Phase IGBT Driving             |

| 16  | V <sub>S(V)</sub>   | High - side Bias Voltage Ground for V Phase IGBT Driving      |

| 17  | IN <sub>(WH)</sub>  | Signal Input for High-side W Phase                            |

| 18  | Vcc                 | Supply Voltage for Driver IC                                  |

| 19  | V <sub>B(W)</sub>   | High - side Bias Voltage for W Phase IGBT Driving             |

| 20  | V <sub>S(W)</sub>   | High - side Bias Voltage Ground for W Phase IGBT Driving      |

| 21  | Nu                  | Negative DC-Link Input for U Phase                            |

| 22  | Nv                  | Negative DC-Link Input for V Phase                            |

| 23  | Nw                  | Negative DC-Link Input Terminal for W Phase                   |

| 24  | U                   | Output for U Phase                                            |

| 25  | V                   | Output for V Phase                                            |

| 26  | W                   | Output for W Phase                                            |

| 27  | Р                   | Positive DC – Link Input                                      |

# 2.1.2 Pin Descrition

# Supply source of the ID- IPM

Pin symbol:  $V_{CC}$

- · V<sub>CC</sub> is internal connected together.

- It is necessary to mount (as possible as close to these pins) a capacitor of favorable frequency to prevent malfunction caused by the unstable operation.

- To prevent damage the internal driver IC. So, it is necessary to keep the operation supply voltage below the maximum specified values.

# Grounding port

Pin symbol: COM

- This is the driver ground for the internal driver IC.

- Main loop current of the power circuit loop should not be allowed to flow through these terminals to avoid noise influences.

# Short-circuit trip voltage sensing port

Pin symbol:  $C_{\text{SC}}$

- The designer need to insert the current sensing resistor between this terminal and GND to detect OC/SC situations.

- The port may recognize the noise as the real input, so the designer need to add a suitable RC filter to reduce the noise level but don't delay the actual signal.

# Fault pulse output time setting port

Pin symbol:  $C_{FOD}$

- This port is used for setting the fault pulse output time.

- In order to set the fault pulse output time, the designer may need to add an external capacitor between this port and ground (reference).

External RC network input used to define FAULT CLEAR delay, TFO, approximately equal to R\*C. When RCIN>8V, the FAULT pin goes back into open-collector high-impedance.

# Fault output port

Pin symbol:  $V_{FO}$

- This terminal will be pulled down to low level in case abnormal condition SC/OC and under-voltage lockout protection is active.

- <sup>•</sup> Because the port is a open collector topology. The signal fit to the FO port is recommended to pulled up to the 5V power supply with approximately  $4.7K \Omega$  resistance.

# **Control input port**

Pin symbol:  $IN_{(UH)}$ ,  $IN_{(VH)}$ ,  $IN_{(WH)}$ ,  $IN_{(UL)}$ ,  $IN_{(VL)}$ ,  $IN_{(WL)}$

- Active logic corresponding to the state of the IGBT.

- \* These pins are input port which is used to detect the controlling pattern to active the IGBT for switching.

- To put RC filter in front of the input port is recommended.

- In order to eliminate the noise when the signal level is changing its state, the trace from controller to the port is recommended as short as possible.

# High-side drive supply port / High-side drive supply reference port

Pin symbol:  $V_{B(U)} V_{S(U)}, V_{B(V)} V_{S(V)}, V_{B(W)} V_{S(W)}$

- \* The bootstrap circuit scheme is needed for driving high side IGBTs by using single supply source.

- $\cdot$  B(x)-S(x) means the input voltage terminal for high-side IGBTs.

- It is necessary to mount(as possible as close to these pins) a capacitor of favorable frequency to prevent malfunction caused by the unstable operation.

# Inverter positive power supply port

Pin symbol: P

- DC-Link positive terminal connected to the collectors of the high-side IGBTs internally.

- Effectively to add a good frequency characteristic capacitor to reduce the voltage spike result in persist inductance of the trace or wiring. And the smoothing capacitor is recommended to put as close to the P and N.

# **Inverter GND port**

Pin symbol:  $N_U, N_V, N_W$

- DC-Link negative terminal connected to the emitters of the low-side IGBTs internally.

- $^{\ast}$  N $_{\rm U}$  :Negative DC-Link Input for U Phase.

- \* Nv :Negative DC-Link Input for V Phase.

- ' Nw :Negative DC-Link Input for W Phase.

# Inverter power output port

Pin symbol: U, V, W

Inverter output port which is used to connect to three phase load, ex induction motor or DC Brush less motor...etc.

• Each terminal is internally connected to the intermediate point of the corresponding IGBT half bridge arm.

# 2.2 Static Characteristics

Table 2-2. Characteristics of ID- IPM (ID20FT06A1S)

| Parameter                               | Symbol                | Condition                                                                              | Min. | Тур. | Max. | Unit |

|-----------------------------------------|-----------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| Collector-emitter<br>breakdown voltage  | $V_{\text{CES}}$      | V <sub>SC</sub> =5V, I <sub>C</sub> =500µA                                             | 600  |      |      | V    |

| Collector-emitter<br>saturation voltage | V <sub>CE (sat)</sub> | V <sub>CC</sub> =15V, V <sub>SC</sub> =0V, I <sub>C</sub> =20A,<br>T <sub>C</sub> =25℃ |      |      | 2.3  | V    |

| FWD forward voltage drop                | V <sub>F</sub>        | $V_{SC}$ =5V, -I <sub>C</sub> =20A, T <sub>C</sub> =25 $^{\circ}$ C                    |      |      | 2.1  | V    |

| Collector-Emitter cut-off<br>current    | Ices                  | V <sub>SC</sub> =5V, V <sub>CE</sub> =600V                                             |      |      | 100  | μA   |

Table 2-3. Characteristics of ID- IPM control part (ID20FT06A1S)

| Item                                                                                                                    | Symbol                                              | Condition                                  | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|------|------|------|------|

| IN <sub>(UH<sup>、</sup>VH<sup>、</sup>WH)</sub> , IN <sub>(UL<sup>、</sup>VL<sup>、</sup>WL)</sub><br>ON threshold voltage | V <sub>IN (on)</sub>                                |                                            | 2.5  |      |      | V    |

| IN <sub>(UH, VH, WH)</sub> ,IN <sub>(UL, VL, WL)</sub><br>OFF threshold voltage                                         | V <sub>IN(off)</sub>                                |                                            |      | 1    | 0.8  | V    |

| IN <sub>(UH VH WH)</sub> input bias                                                                                     | I <sub>IN(UH<sup>、</sup>VH<sup>、</sup>WH)(HI)</sub> | V <sub>IN(UH、VH、WH)</sub> = 5V             | -    | -    | 200  |      |

| current                                                                                                                 | $I_{IN(UH^{\vee}VH^{\vee}WH)}(LO)$                  | V <sub>IN(UH, VH, WH)</sub> = 0V           | -1   | I    | -    | μA   |

| IN(UL, VL, WL) input bias current                                                                                       | I <sub>IN(UL、VL、WL)</sub> (HI)                      | V <sub>IN(UL`VL`WL)</sub> = 5V             | -    | -    | 200  | μA   |

|                                                                                                                         | I <sub>IN(UL、VL、WL)</sub> (LO)                      | $V_{IN(UL_{VL_{VL_{VL}}}WL)} = 0V$         | -1   | -    | -    | μΛ   |

| Driver IC supply voltage                                                                                                | V <sub>CC</sub>                                     |                                            | 11.5 | 15.0 | 20.0 | V    |

| P - side floating supply<br>voltage                                                                                     | $V_{B(U)S(U),\;B(V)S(V),\;B(W)S(W)}$                |                                            | 11.5 | 15.0 | 20.0 | V    |

| V <sub>cc</sub> terminal input current                                                                                  | I <sub>C</sub>                                      |                                            | -    | 1.6  | 2.3  | mΑ   |

| Eault output voltago                                                                                                    | V <sub>FOH</sub>                                    | V <sub>SC</sub> =0V                        | 4.9  | -    | -    | V    |

| Fault output voltage                                                                                                    | V <sub>FOL</sub>                                    | V <sub>SC</sub> =1V                        | -    | -    | 200  | mV   |

| Short circuit trip level                                                                                                | V <sub>SC(ref)</sub>                                | V <sub>CC</sub> =15V, T <sub>i</sub> = 25℃ | 0.45 | 0.50 | 0.55 | V    |

| Fault output pulse width                                                                                                | t <sub>FOD</sub>                                    | С <sub>F О D</sub> = 33nF                  | -    | 1.8  | -    | ms   |

| Supply circuit under voltage                                                                                            |                                                     | Trip level                                 | 8.6  | 9.4  | 10.2 | V    |

| protection                                                                                                              | U <sub>VCCR</sub>                                   | Detection level                            | 9.6  | 10.4 | 11.2 | V    |

| protection                                                                                                              | UVH                                                 | Hysteresis                                 | -    | 1.0  | -    | V    |

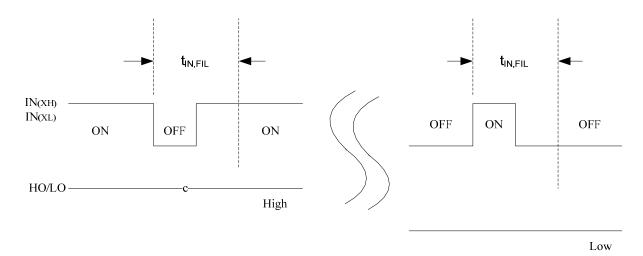

| $IN_{(UL^{,}\ VL^{,}\ WL)}$ Input filter time                                                                           | t <sub>IN,FIL</sub>                                 | VIN = 0 & 5V                               | 100  | 200  | -    | ns   |

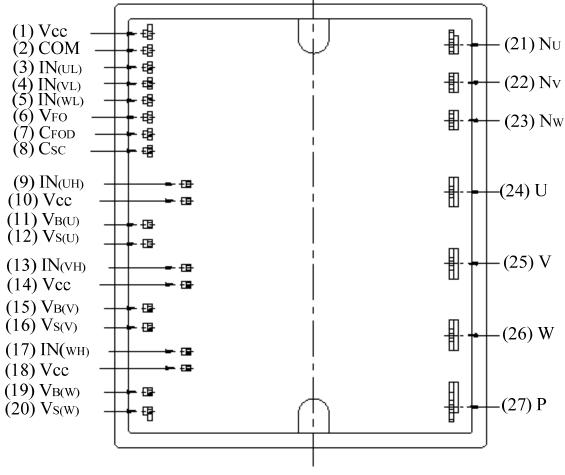

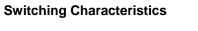

# 2.3 Dynamic Characteristics

# Table 2-4. Characteristics of ID- IPM (used ID20FT06A1S as the example)

| Parameter       | Symbol           | Condition                                                                                                           | Min. | Тур. | Max. | Unit |   |      |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|---|------|

|                 | T <sub>on</sub>  | $V_{CE}$ =300V, $V_{CC}$ =15V, $I_{C}$ =20A,<br>$V_{IN(UH)} = V_{IN(VH)} = V_{IN(WH)} = 0V$ →<br>5V, $T_{C}$ =25 °C |      | 1.08 | -    |      |   |      |

| Switching times | Tr               |                                                                                                                     |      | 0.20 |      |      |   |      |

|                 | Tc(on)           |                                                                                                                     |      | 0.32 | -    |      |   |      |

|                 | T <sub>off</sub> |                                                                                                                     |      | 0.98 |      | μs   |   |      |

|                 | T <sub>f</sub>   |                                                                                                                     |      | 0.06 | -    |      |   |      |

|                 | Tc(off)          |                                                                                                                     |      |      |      |      | - | 0.50 |

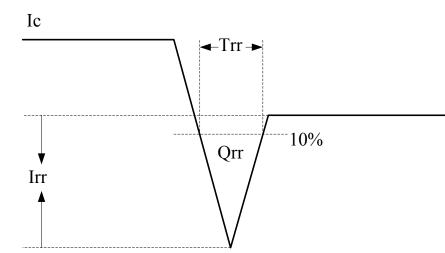

|                 | Trr              |                                                                                                                     |      | 0.13 | -    |      |   |      |

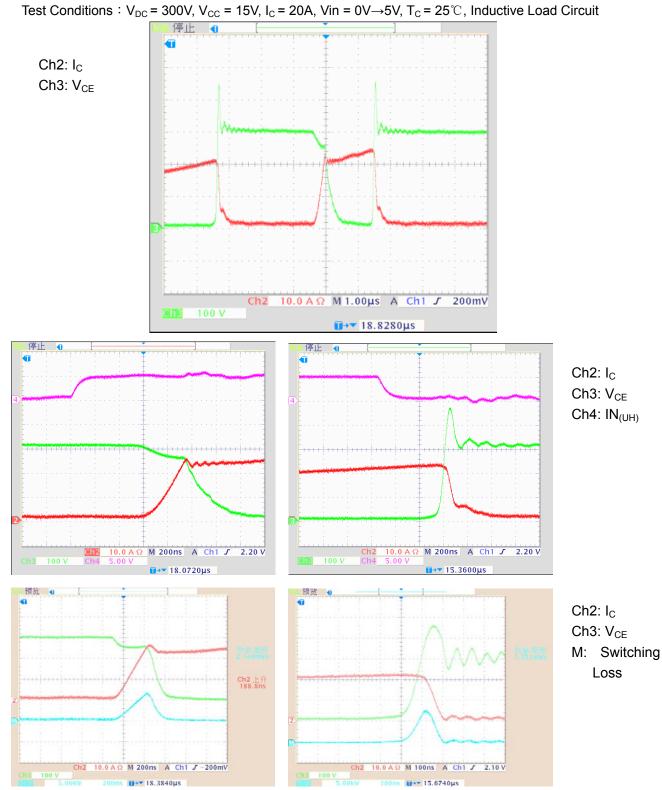

Figure 2-2. Definition of Switching Time

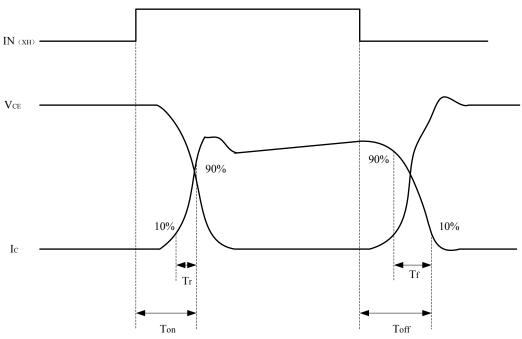

Figure 2-3. Evaluation Circuit Diagram (Inductive Load)

Note:  $V_{BS1} = V_{BS2} = V_{BS3} = Vcc = 15V$

Figure 2-4. Test Circuit of Dynamic Parameter

Figure 2-5. Switching Time Definition

# 嘉兴斯达半导体有限公司

# STARPOWER SEMICONDUCTOR LTD.

Figure 2-6. Switching Waveform of ID- IPM (Used ID20FT06A1S class) (Typ.)

# Chapter 3 Packaging and Installation Guide

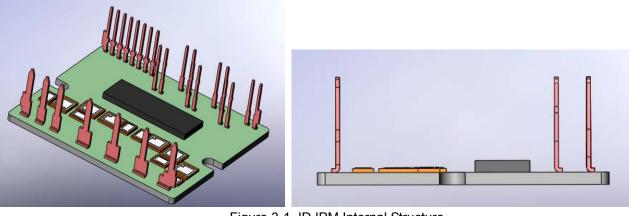

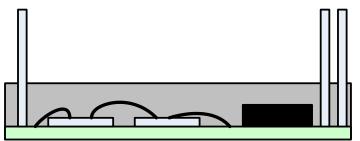

- 3.1 Package

- 3.1.1 Internal Structure Overview

Figure 3-1. ID IPM Internal Structure

# 3.1.2 Driving and Protection Functions

# **Driving logic**

- <sup>•</sup> When the logic level of  $IN_{(xH)}$  or  $IN_{(xL)}$  is in high state then its corresponding IGBT will be "ON". And when  $IN_{(xH)}$  or  $IN_{(xL)}$  is in low state then its corresponding IGBT will be "OFF".

- <sup>•</sup> Under-Voltage protection: if the input level of  $V_{IN(xH) \& IN(xL)}$  is higher than  $V_{th(on)}$  then IPM will work normally, If the input level of  $V_{IN(xH) \& IN(xL)}$  is lower than  $V_{th(off)}$ , then IPM will shut-off its output.

# Short circuit protection

- Usually the designer will use external shunt resistance to detect the injection DC-Link current to protect the load. When the current exceeds a preset SC trip level, it is judged as a short circuit state, and IPM will shut off its output immediately.

- Once the current is over the current limitation passing through the external shunt resistance. A fault pulse signal will output and the pulse duration will be determined by the capacitance of the capacitor connected between C<sub>FOD</sub> and COM. After it is being outputted continuously for a certain period of time (depends on the capacitor), fault condition will be reset when the next input signal reaches the normal level.

# Control supply circuit under voltage protection

- The protection is used to make sure the control supply voltage for high/low-side IGBT driving. Input signals to the high/low-side IGBTs are locked if the voltage falls below the trigger level for a given period of time.

- Only when the voltage exceeds the reset level of under-voltage protection, under-voltage protection won't be reset.

· Under-voltage protection fault pulse signal output period is determined by the capacitance of

the external capacitor that is connected between  $C_{FOD}$  pin and COM pin. After fault signal is being outputted for a certain period of time, and the time is depends on the capacitor and the voltage level. The fault resetting takes place at the next input signal if the control supply voltage is over the reset level.

# 3.2 Installation Guide

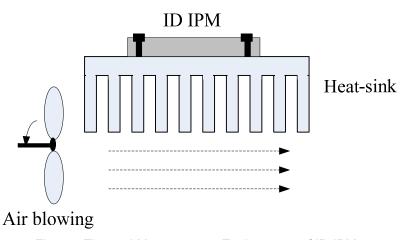

# 3.2.1 Heat Sink Mounting

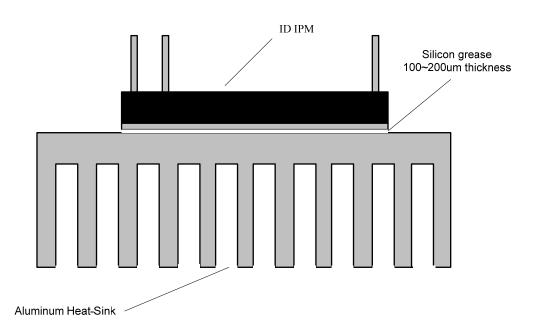

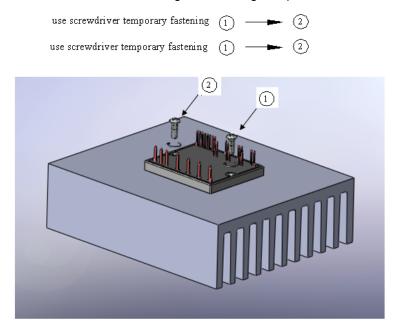

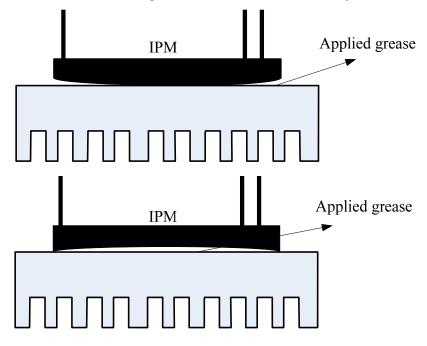

The following precautions should be observed to maximize the effect of the heat sink and minimize device stress, when mounting an ID- IPM on a heat sink. When apply silicon grease between the ID- IPM and the heat sink to reduce the contact thermal resistance. Be sure to apply the coating thinly and evenly, do not use too much. A uniform layer of silicon grease ( $100 \sim 200$ um thickness) should be applied in this situation. Fig. 3-3 shows the recommended silicon grease thickness.

Figure 3-3. Recommended Silicon Grease Thickness

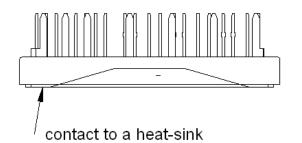

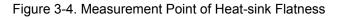

When attaching a heat-sink to an ID- IPM. Make sure not to apply excessive force to the device for assembly. Drill holes for screws in the heat sink exactly as specified. Smooth the surface by removing burrs and protrusions of indentations. Do not touch the heat-sink when IPM is operation to avoid sustaining a burn injury. Table 2-2 can provide the designer the guideline. Heat sink flatness is prescribed as seen in Figure 2-4.

# Table 3-1. Mounting Torque and Heat Sink Flatness Specifications

| Item               | Condition          |                      |      | Тур. | Max. | Unit |

|--------------------|--------------------|----------------------|------|------|------|------|

| Mounting torque    | Mounting screw: M3 | Recommended 0.65 N•m | 0.60 | 0.65 | 0.70 | N•m  |

| Heat-sink flatness |                    |                      | -50  | -    | 0    | μm   |

20

# 3.2.2 Screw Tightening Torque

Do not exceed the specified fastening torque. Over tightening the screws may cause molding compound crack and bolts with heat-fin destruction. Tightening the screws beyond a certain torque can cause saturation of the contact thermal resistance. The tightening torques in table 2-2 is recommended for obtaining the proper contact thermal resistance and avoiding the application of excessive stress to the device. Avoid stress due to

**ID-Series IPM Applicaton Note**

tightening on one side only. Figure 2-5 shows the recommended fastening order for mounting screws. In the first use screwdriver temporary fastening screws, then use screwdriver permanent fastening. Note that uneven mounting can cause the ID-IPM housing and molding compound to be damaged.

Figure 3-5. Recommended Fastening Order of Mounting Screws

The heat sink flatness (warp/concavity and convexity) on the module installation surface (refer to Figure 2-6), please follow the guidelines below in order to get effective heat-radiation when you want to enlarge the heat area.

Figure 3-6. Heat Sink Flatness Specification

It will get better  $100\mu m \sim 200\mu m$  of thermally-conductive grease over the contact surface between a module and a heat sink. It is also useful for preventing the contact surface from being corroded. Further, use a grease type of stable quality within the operating temperature range and have long endurance. Use a torque wrench to fasten up to the specified recommended torque. Exceeding the max data, torque limit might cause the modules to be damaged or to be degraded as the above-mentioned fastening with uneven stress. Foreign matter onto the contact surface between a module and a heat sink will be worse the contacting.

# 3.3 Handling Precaution and Storage Notices

When using semiconductors, the incidence of thermal and/or mechanical stress to the devices due to improper handling may result in significant deterioration of their electrical characteristics and/or reliability.

# Transportation

Be careful to handle the device and packaging material. Ensure that the device is not subjected to mechanical vibration or shock during transport. Do not toss or drop to ensure the device is O.K before on board. Wet condition is dangerous. Moisture can also adversely affect the packaging. Place the devices in the conductive trays before using. Hold the package and avoid touching the leads when handling devices. Do pay attention to the gate terminal. Put package boxes upside down, leaning them or giving them uneven stress might cause the electrode terminals to be deformed or the resin case to be damaged. Throwing or dropping the packaging boxes might cause the devices to be damaged. Wetting the packaging boxes might cause the breakdown of devices when operating. Pay attention not to wet them when transporting on a rainy or a snowy day.

# Storage

- Force or load the external pressure to the devices is not allowable.

- The storage area which will make the devices to be exposed to moisture or direct sunlight is not acceptable.

- The humidity should be kept within the range from 40% to 75%, and the temperature should be kept within the range from 5°C to 35°C.

- In the presence of harmful gases or in dusty conditions is not acceptable for storage.

- Lead solder ability will be degraded cause by lead oxidation or corrosion. So to use storage areas where there is minimal temperature fluctuation is highly recommended.

- Use antistatic containers. Unused devices should be stored no longer than one month when repacking devices.

# Environment

- Use a board container or bag that is protected against static charge in case when storing device-mounted circuit boards.

- Do not stack them directly on top of one another, and keep them separated from each other, and to prevent static charge/discharge which occurs due to friction.

- Be sure cart surfaces that come into contact with device packaging are made of materials that will conduct static electricity, and are grounded to the floor surface with a grounding chain.

- To wear finger cots or gloves protected against static electricity if the human body comes into direct contact with a device,

- When humidity in the working environment decreases, the human body and other insulators can easily become charged with electrostatic electricity due to friction. Maintain the recommended humidity of 40% to 60% in the work environment. Be aware of the risk of moisture absorption by the products after unpacking from moisture-proof packaging.

- All equipment and tools in the working area are grounded to earth is necessary.

- Take other appropriate measures, or place a conductive mat over the floor of the work area, or so that the floor surface is grounded to earth and is protected against electrostatic electricity.

- Cover the workbench surface with a conductive mat, grounded to earth, to disperse electrostatic electricity on the surface through resistive components. Workbench surfaces must not be constructed of low-resistance metallic material that allows rapid static discharge when a charged device touches it directly.

- Ensure that work chairs are protected with an antistatic textile cover and are grounded to the floor surface with a grounding chain.

- Install antistatic mats on storage shelf surfaces.

- For transport and temporary storage of devices, use containers that are made of antistatic materials of materials that dissipate static electricity.

- Operators must wear antistatic clothing and conductive shoes (or a leg or heel strap).

- Operators must wear a wrist strap grounded to earth through a resistor of about 1M  $\Omega$ .

- If the tweezers you use are likely to touch the device terminals, use an antistatic type and avoid metallic tweezers. If a charged device touches such a low-resistance tool, a rapid discharge can occur. When using vacuum tweezers, attach a conductive chucking pad at the tip and connect it to a dedicated ground used expressly for antistatic purposes.

# **Electrical Shock**

• Do not touch the device unless you are sure that the power to the measuring instrument is off to avoid electrical measurement poses the danger of electrical shock for the device.

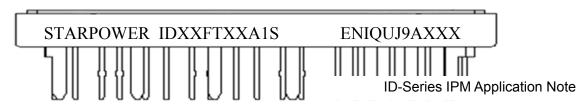

# 3.4 Marking Specification

Figure 3-7. Marking Layout

- 1. IDXXFTXXA1S : ID series modeling ex:ID20FT06A1S sepc ID IPM 600V 20A

- 2. ENIQUJ9AXXX: Lot number ex:ENIQUJ9A003 ID 2009 08 3th Number

# **Chapter 4** Applications

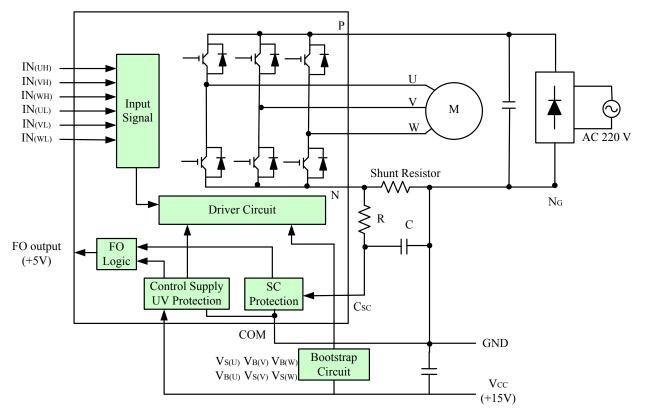

# 4.1 System Connection Diagram

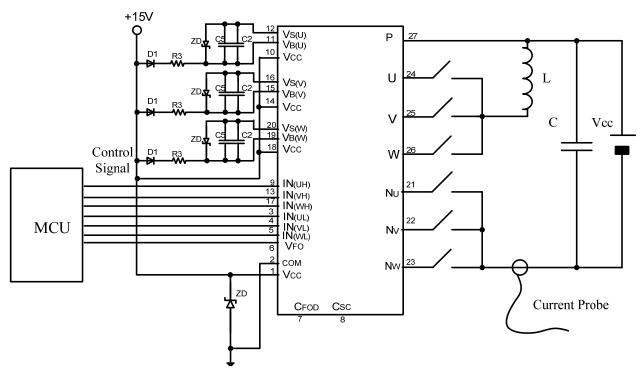

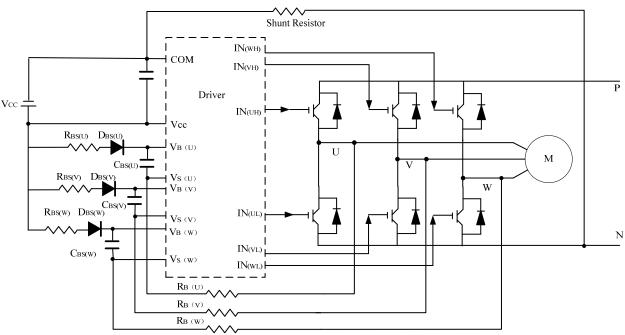

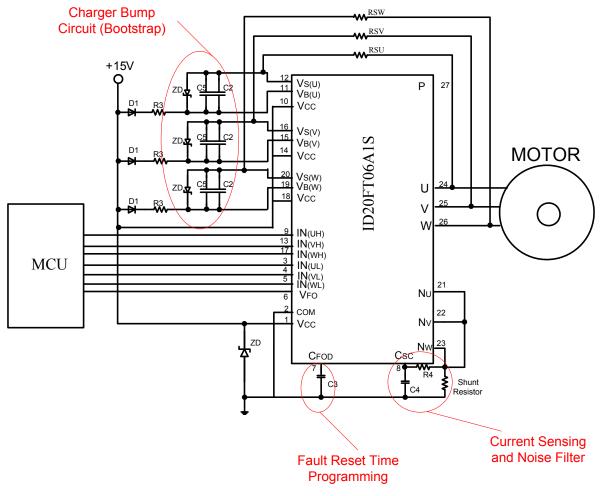

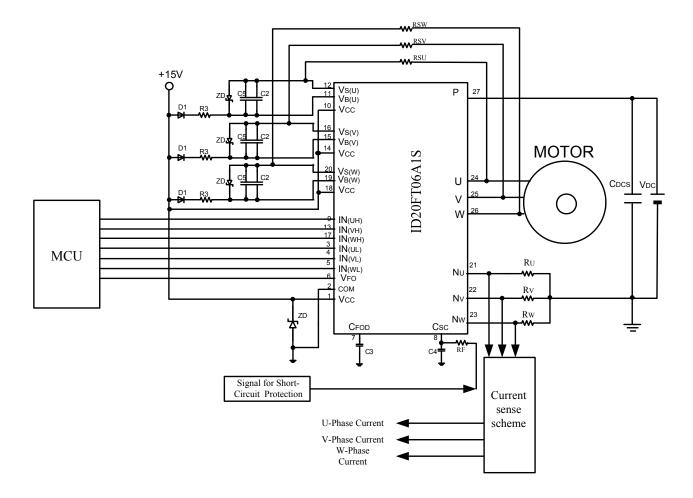

Figure 4-1. System Block Diagram of the IPM

# 4.2 Structure of Signal Input Terminals

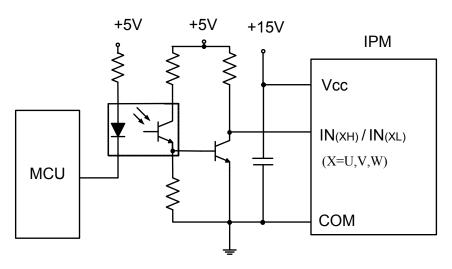

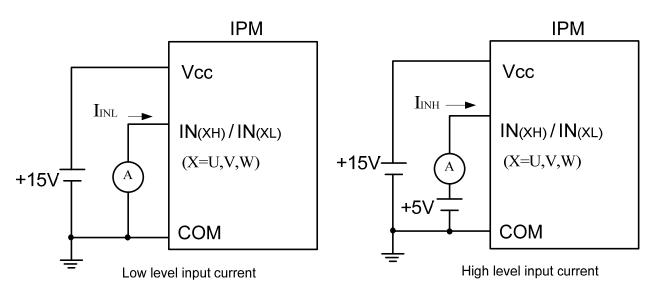

Figure 4-2. Interface Circuit Between ID-IPM and MCU

Note: RC coupling at each input may be changed depending on the PWM control scheme used in the application and on the wiring impedances of the application's PCB.

### **Signal Input and Fault Output**

The structure of IPM signal input terminals is shown in Figure 4-2. The Fault output FO and input signals of the IPM should be a 5V-class interface. Therefore, if an opto-coupler is used, its supply voltage should be 5V. The maximum ratings for input and fault output voltages are shown in Table 4-1 and 4-2. As fault output is an open collector type and it's rating is 20.3V, 15V-class supply is possible. However, 5V-class supply is recommended for the fault output same as the input signals.

| Item                 | Symbol                                     | Condition                                         | Ratings   | Unit |  |  |  |  |

|----------------------|--------------------------------------------|---------------------------------------------------|-----------|------|--|--|--|--|

| Input signal voltage | V <sub>IN(XH)</sub><br>V <sub>IN(XL)</sub> | Applied between $IN_{(XH)} - COM IN_{(XL)} - COM$ | -0.3 ~ +5 | V    |  |  |  |  |

| Fault output voltage | $V_{\text{FO}}$                            | Applied between FO – COM                          | -0.3 ~ +5 | V    |  |  |  |  |

Table 4-1. Maximum Ratings of Input Signal and FO Pins Voltage

### Table 4-2. Value of Input Signal Current

| Item                                          | Symbol              | Condition               | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|---------------------|-------------------------|------|------|------|------|

| IN <sub>(UH / VH / WH)</sub><br>input current | I <sub>IN(HI)</sub> | $V_{IN(UH/VH/WH)} = 5V$ | -    | 100  | 200  |      |

|                                               | I <sub>IN(LO)</sub> | $V_{IN(UH/VH/WH)} = 0V$ | -1   | -0.5 | -    |      |

| IN <sub>(UL / VL / WL)</sub><br>input current | I <sub>IN(HI)</sub> | $V_{IN(UL/VL/WL)} = 5V$ | -    | 100  | 200  | μA   |

|                                               | I <sub>IN(LO)</sub> | $V_{IN(UL/VL/WL)} = 0V$ | -1   | -0.5 | -    |      |

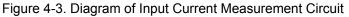

# 4.3 Bootstrap Circuit

Power for the high side gate drive is normally supplied using external bootstrap circuits. The bootstrap circuit typically consists of a low current 600V fast recovery diode with a small series resistor to limit the peak charging current and a floating supply reservoir capacitor. In order to avoid transient voltages and oscillations on the floating power supplies it is often desirable to add a low impedance film or ceramic type capacitor in parallel with each floating supply reservoir capacitor.

# 4.3.1 Operation of a Bootstrap Circuit

The  $V_{BS}$  voltage, which is the voltage difference between  $V_B$  and  $V_S$ , provides the supply to the driver IC within the IPM. This supply must be in the range of 10~20V to ensure that the driver IC can fully drive the high-side IGBT. The IPM includes an under-voltage detection function for the  $V_{BS}$  to ensure that the driver IC does not drive the high-side IGBT, if the  $V_{BS}$  voltage drops below a specified voltage (refer to the datasheet). This function prevents the IGBT from operating in a high dissipation mode.

The bootstrap circuits is formed by an external ultra fast diode  $D_{BS}$ , capacitor  $C_{BS}$  and resistor  $R_{BS}$ . The bootstrap capacitor  $C_{BS}$  charges through the bootstrap diode  $D_{BS}$  and resistor  $R_{BS}$  from the V<sub>CC</sub> supply when the high-side IGBT is off, and the V<sub>S</sub> voltage is pulled down to ground. It discharges when the high-side IGBT is on. The current flow path of the bootstrap circuit is shown in Figure 4-4. It is necessary to apply an enough pulse width to fully charge the bootstrap capacitor  $C_{BS}$  and the timing chart of Initial bootstrap operation charging is shown in Figure 4-5.

Figure 4-4. Bootstrap Circuit

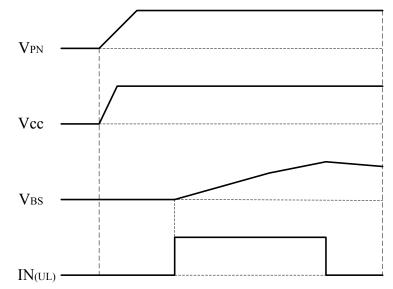

Figure 4-5. Timing Chart of Initial Bootstrap Operation Charging

The bootstrap capacitor charging and discharging timing chart is shown as Fig 4-7. We can see that the voltage  $V_{BS}$  is not a pure DC level and it has an inherently fluctuating voltage waveform because it is a floating supply due to bootstrap action.

Figure 4-6. Inverter Circuit Diagram

Figure 4-7. Charging and Discharging Action of the Bootstrap Capacitor Timing Chart

### 4.3.2 Initial Charging of a Bootstrap Capacitor

An adequate on-time duration of the low-side IGBT to fully charge the bootstrap capacitor is required for initial bootstrap charging. The initial charging time  $t_{charge}$  can be calculated from the following equation:

$$t_{\text{charge}} \ge C_{\text{BS}} \times R_{\text{BS}} \times \frac{1}{\delta} \times \ln \left( \frac{V_{\text{CC}}}{V_{\text{CC}} - V_{\text{BS(min)}} - V_{\text{F}} - V_{\text{LS}}} \right)$$

(4-1)

$V_{F}$  = Forward voltage drop across the bootstrap diode

$V_{BS(min)}$  = The minimum value of the bootstrap capacitor

V<sub>LS</sub> = Voltage drop across the low-side IGBT or load

$\delta$  = Duty ratio of PWM

### 4.3.3 Bootstrap Capacitor Selection

The voltage source of the bootstrap capacitor is the Vcc supply. Its capacitance is determined by the following constraints:

- 1. The gate charge required to enhance the IGBT.

- $2 \ I_{QBS}$  Quiescent current for the driver IC.

- 3、Currents within the level shiftier of the driver IC.

- 4. Bootstrap capacitor leakage current.

Factor 4 is only relevant if the bootstrap capacitor is an electrolytic capacitor. It can be ignored if other types of capacitors are used. Hence, it is always better to use a non-electro ID-Series IPM Application Note<sub>tion</sub> describes the minimum charge, which needs to be supplied by the bootstrap capacitor:

$$Q_{BS} \ge Q_g + \frac{I_{GE(leakage)} + I_{CBS(leak)}}{f} + Q_{LS}$$

(4-2)

$$\begin{split} & Q_g = \text{Gate charge of the high-side of the IGBT} \\ & f = \text{Switching frequency} \\ & I_{\text{CBS(leak)}} = \text{Bootstrap capacitor leakage current} \\ & I_{\text{GE(leakage)}} = \text{Gate to emitter leakage current for the driver IC} \\ & Q_{\text{LS}} = \text{Level shift charge required per cycle} = 5nC(\text{built in driver IC}) \end{split}$$

The bootstrap capacitor must be able to supply this charge  $Q_{BS}$ , and retain its full voltage. Otherwise, there will be a significant amount of ripple on the  $V_{BS}$  voltage, which could fall below the  $V_{BSUV}$  (under-voltage detection level). Hence, it is recommended that the charge in the  $C_{BS}$  capacitor be at least twice the above value. Due to the nature of bootstrap circuit operation, a low value capacitor can lead to overcharging, which could in turn damage the driver IC. The minimum bootstrap capacitor value can be obtained from the following equation (4.3). Recommend to put the experienced value from 10uF~22uF.

$$C_{BS} \ge \frac{\left[Q_{g} + \frac{I_{GE(leakage)} + I_{CBS(leak)}}{f} + Q_{LS}\right]}{\Delta V}$$

(4-3)

Where  $\Delta V$  = the allowable discharge voltage of the C<sub>BS</sub>.

Note that the following equation (4.4) should be used for a specific system application, with an extended period of application of the standstill mode of the PWM output, during the changing of the rotor direction.

$$C_{BS} \ge I_{BS} \times \Delta T / \Delta V \tag{4-4}$$

Where  $\triangle T$  is the maximum ON pulse width of IGBT1 and  $I_{BS}$  is the drive current of the driver IC (depends on temperature and frequency characteristics), and  $\triangle V$  is the allowable discharge voltage.

The bootstrap capacitor should always be placed as close to the pins of the IPM as possible. A separate ceramic capacitor close to the IPM would be essential if an electrolytic capacitor were used for the bootstrap capacitor. Using a ceramic or tantalum type for the bootstrap capacitor, it should be adequate for local decoupling.

# 4.3.4 Series Resistor Selection

A resistor  $R_{BS}$  must be added in series with the bootstrap in ID-Series IPM Application Note the series resistor relative to the value of the bootstrap capacitor should be chosen such that the RC time constant is equal to or greater than 10us. Note that if the rising  $dV_{BS}/dt$  is slowed down significantly, it could temporarily result in a few missing pulses during the start-up phase due to insufficient  $V_{BS}$  voltage.

Resistor  $R_{BS}$  should be basically selected such that the time constant  $R_{BS} \times C_{BS}$  will enable the discharged voltage  $\triangle V$  being charged again into  $C_{BS}$  within the maximum ON pulse width of IGBT2, as show figure 4.7. However, if only IGBT1 has an ON-OFF-ON control mode, the time constant should be set so that the consumed charge during the ON period can be charged during the OFF period.

# 4.3.5 Bootstrap Diode Selection

The bootstrap diode  $D_{BS}$  is used for blocking the inverter DC-link voltage when the high-side device is switched "ON. So the bootstrap diode with withstand-voltage more than 600V is recommended. It is also important that the diode should be an ultra-fast recovery device to minimize the amount of charge that is fed back from the bootstrap capacitor into the V<sub>CC</sub> supply. Similarly, the high temperature reverse leakage current would be important if the capacitor has to store a charge for long periods of time.

# 4.4 Application Circuit and Recommended Parts

# 4.4.1 Direct Input (without photo-Coupler) Interface Example

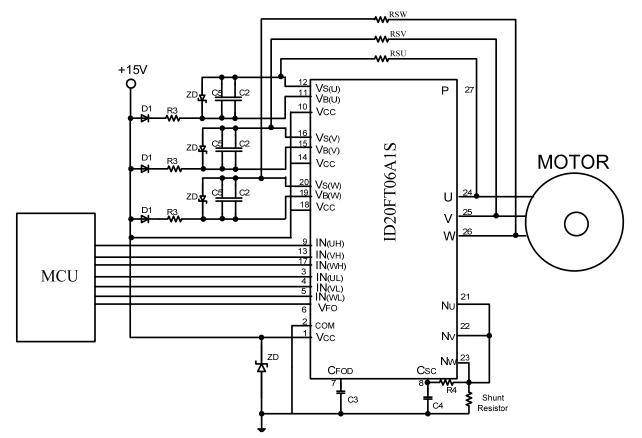

Figure 4-8. Typical Application Circuit Interface Example with Direct Input (Without Photo-Coupler)

### Component selection:

- 1. R3 : 20  ${}^{\Omega}$  ( It could be adjusted depending on the PWM frequency. )

- 2. R4 : 100  $\Omega$   $\,$  ( Recommended the time constant R4xC4 is 2  $\mu$  S. )

- 3. C2 : 10 ~ 100  $\mu$  F ( Electrolytic, low impendence )

- 4. C3 : 22~33nF ( Ceramic )

- 5. C4 : 22~33nF ( Ceramic )

- 6. C5 : 0.22 ~ 2  $\mu$  F ( Ceramic )

- 7. D1:600V/1A (Ultra-Fast recovery diode )

# 4.4.2 Interface Example When a Photo-Coupler is Used

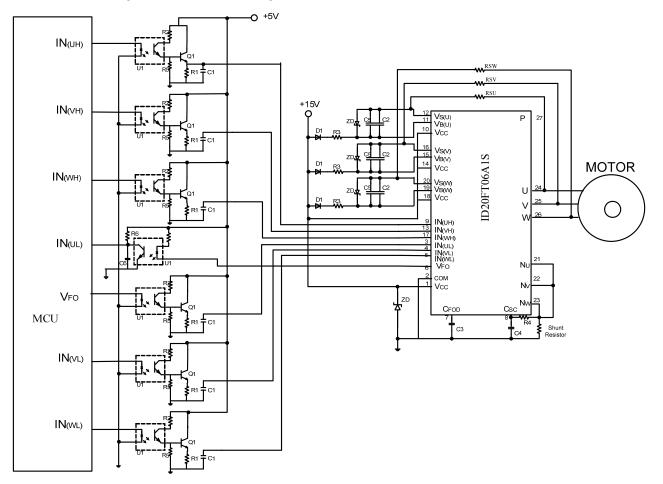

Figure 4-9. Typical Application Circuit Interface Example with Photo-Coupler

# Component selection:

| 1.R1 : | 4.7ΚΩ                                                              |

|--------|--------------------------------------------------------------------|

| 2.R2 : | <b>150</b> Ω                                                       |

| 3.R3 : | $20 \Omega$ (It could be adjusted depending on the PWM frequency.) |

| 4.R4 : | 100 $\Omega$ (Recommended the time constant R4xC4 is 2 $\mu$ S.)   |

| 5.R5 : | 1ΚΩ                                                                |

| 6.R6 : | 1ΚΩ                                                                |

| 7.R7 : | 1ΚΩ                                                                |

| 8.C1 : | 0.1 µ F                                                            |

| 9.C2 : | $10 \sim 100 \mu$ F ( Electrolytic, low impendence )               |

| 10.    | C3 : 22~33nF ( Ceramic )                                           |

| 11.    | C4 : 22~33nF ( Ceramic )                                           |

| 12.    | C5 : 0.22 ~ 2 µ F ( Ceramic )                                      |

| 13.    | C6 : 0.1 µ F                                                       |

| 14.    | D1 : 600V/1A ( Ultra-Fast recovery diode )                         |

| 15.    | Q1 : NPN transistor 2N3904                                         |

| 16.    | U1 : Photo coupler TLP521                                          |

|        |                                                                    |

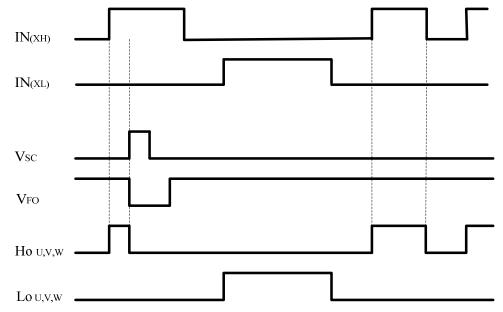

# 4.5 Input / Output Timing Diagram

Note: The shaded area indicates that both high-side and low-side switches are off and therefore the half-bridge output voltage would be determined by the direction of current flow in the load.

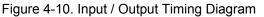

Figure 4-11. Input/Output Signal Circuit

# 4.6 Function and Protection Timing Charts

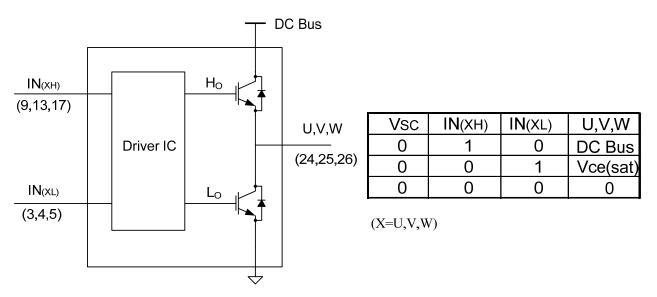

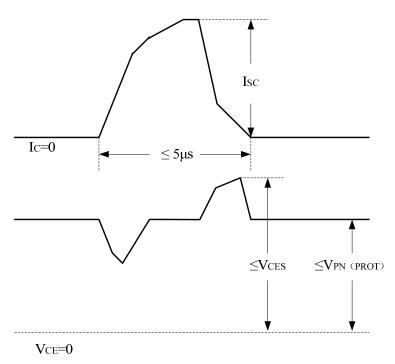

# 4.6.1 Timing Charts of Short Circuit Protection

(For the external shunt resistor and RC time constant circuit connected)

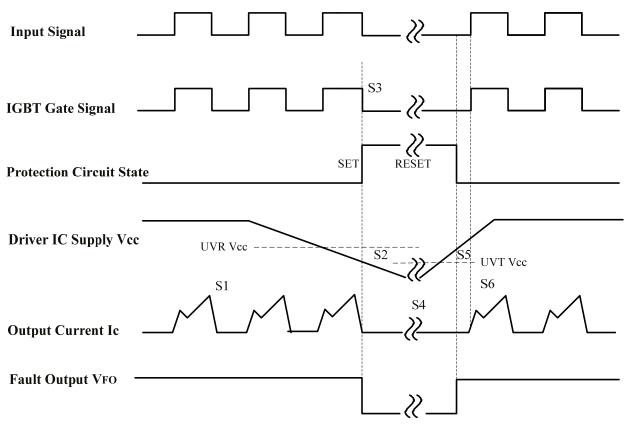

Figure 4-12. Timing Chart of SC Operation

S1. Normal operation : IGBT ON and carrying current.

S2. Short circuit current detection (SC trigger).

- S3. Hard IGBT gate interrupt.

- S4. IGBT turns OFF.

- S5. IGBT OFF signal.

- S6. IGBT ON signal but IGBT cannot be turned on during the fault Output activation

- S7. IGBT OFF state.

- S8. Fault Output reset and normal operation start

# 4.6.2 Timing Charts of Under-voltage Protection

Figure 4-13. Timing Chart of Under-Voltage Operation

- S1. Normal operation : IGBT ON and carrying current

- S2. Under-voltage trip

- S3. IGBT turns OFF inspire of control input condition

- S4. FO timer operation starts : The pulse width of the FO signal is set by the external capacitor.

- S5. Under-voltage reset

- S6. Normal operation : IGBT ON and carrying current

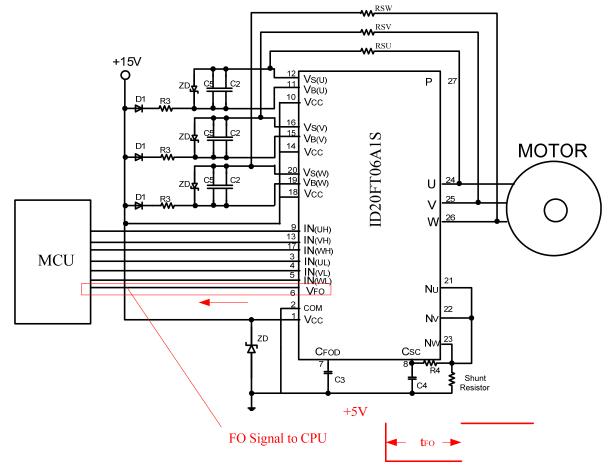

# 4.6.3 Fault Output Loop

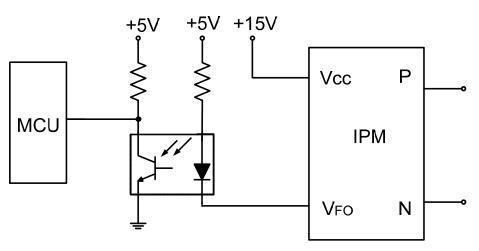

Figure 4-14. Diagram of FO pin Measurement Circuit

# Table 4-4. Maximum Ratings

| Item                 | Symbol | Condition                 | Rating            | Unit |

|----------------------|--------|---------------------------|-------------------|------|

| Fault output voltage | VFO    | Applied between VFO – COM | - 0.3 ~ VCC + 0.5 | V    |

| Fault output current | IFO    |                           | 10                | mA   |

Table 4-5. Electrical Characteristics

| Item                 | Symbol | Condition                           | Min. | Тур. | Max. | Unit |

|----------------------|--------|-------------------------------------|------|------|------|------|

| Fault output voltage | VFOH   | VSC =0V, VFO =4.7k $\Omega$ to 5V   | 4.9  | -    | -    | V    |

|                      | VFOL   | VSC =0.5V, VFO =4.7k $\Omega$ to 5V | -    | -    | 0.2  | V    |

# 4.6.4 Selecting the Current Sensing Shunt Resistor Value

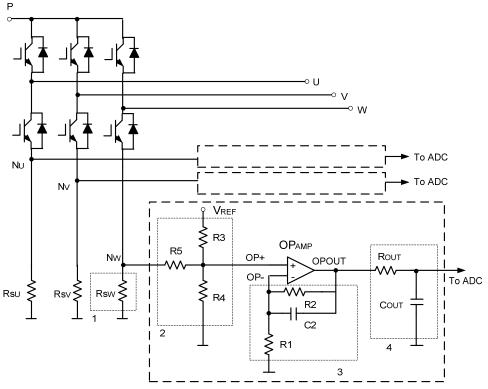

The IPM short circuit protection accepts the voltage value across the external current sensing resistor into the internal driver IC as SC trip level (reference voltage) and operates by internally interrupting the output. The scheme for setting the value of external current sensing resistor is shown below :

The current sensing resistor value is calculated using this expression:

$$R = V_{SC (ref)} / I_{SC}$$

Where  $V_{SC \ (ref)}$  is the SC trip level (reference voltage) of the driver IC and  $I_{SC}$  is the current value to be interrupted

• The SC trip level (reference voltage) of the driver IC is designed based on the following specifications. Therefore, the fluctuation range (shown in Table 4-6.) should be taken into consideration.

36

- 嘉兴斯达半导体有限公司 STARPOWER SEMICONDUCTOR LTD.

- Figure 4-14. shows the relationship between sensing resistor values and interrupted current values, based on various conditions including fluctuation range described in Table 4-6.

- In the actual design, the filter circuit would be necessary and the sensing resistor value should be evaluated.

| Condition                                                              | Min. | Тур. | Max. | Unit |  |

|------------------------------------------------------------------------|------|------|------|------|--|

| $V_{SC(ref)}$ specification at T <sub>a</sub> =25 °C <sub>(Typ.)</sub> | 0.45 | 0.50 | 0.55 | V    |  |

| Table 4-6 | . Specification | for V <sub>SC (ref</sub> |

|-----------|-----------------|--------------------------|

|           | . opcomoutori   |                          |

#### Example:

Sample NO.: ID20FT06A1S (20A/600V)

The maximum recommended short-circuit trip current is 1.7 times the nominal IC rating of the module: lag(max) = lag(max) = 1.7 = 20.14

$lsc(max) = lc(rating) \times 1.7 = 20 \times 1.7 = 34A$

The minimum allowable shunt resistance is determined by requiring that the protection must operate at Ic = 34A, even if the modules short-circuit detection reference level (Vsc(ref)) is at its maximum. Referring to Table 4-6. for Vsc(ref) the minimum shunt resistance is:

Rshunt(min) = Vsc(ref)max / Isc =0.55 / 34 = 16.1 m  $\Omega$

If the tolerance of the shunt resistor is 5% then the possible range is:

Rmin = 16.1 m  $\Omega$ , Rtyp = 17.0 m  $\Omega$ , and Rmax = 17.8 m  $\Omega$

The typical short-circuit trip current is:

Isc(typ) = Vsc(ref)typ / Rtyp = 0.46 / 0.017 = 27.06A

The minimum short-circuit trip current is:

Isc(min) = Vsc(ref)min / Rmax = 0.37 / 0.0178 = 20.78A

Therefore, the range for short-circuit trip current is from 20.78A to 27.06A.

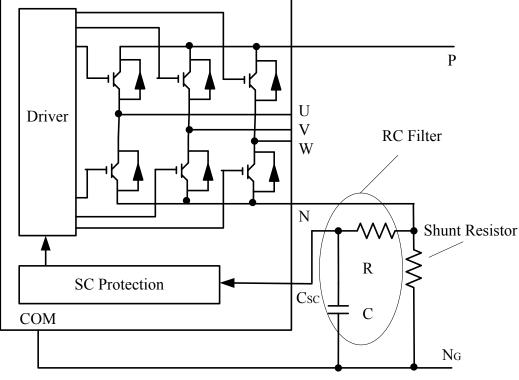

#### 4.6.5 Filter Circuit Setting (RC Time Constant) for Short-Circuit Operation

#### **Example of IPM Short-circuit Protection External Parts**

The IPM have an integrated short-circuit protection function. The driver IC monitors the voltage across an external shunt resistor RSHUNT to detect excessive current in the DC link and provide protection against short circuits.

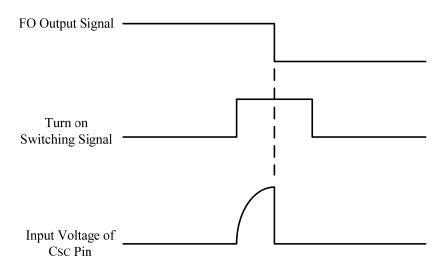

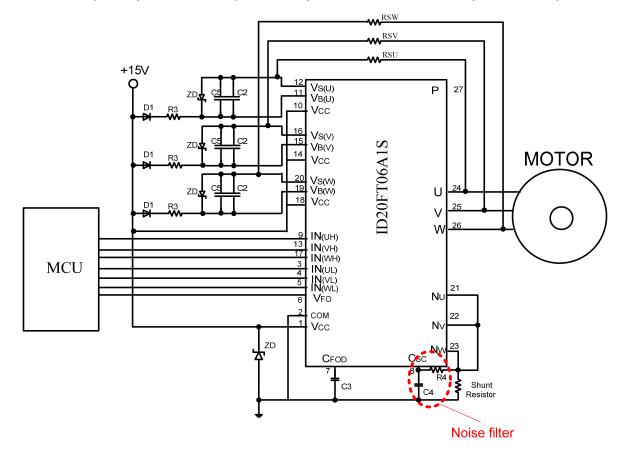

Figure 4-15 illustrates the typical external components used for sensing current. The voltage across RSHUNT is filtered by an RC circuit (R, C) and connected to the CIN pin. If the voltage at the CIN pin exceeds Vsc(ref), which is specified on the devices data sheets, then a fault signal is asserted and the arm IGBTs are turned off. The following sections will provide a detailed description of the over current protection function and external component selection.

Figure 4-15. Example of External RC Filter Circuit

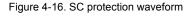

Figure 4-16 shows the example of external SC protection circuit. If the output current exceeds the SC trip level, all the gates of each IGBT are interrupted and the fault signal FO is outputted. The system operation should be stopped immediately when the fault output signal is pulled low.

#### • Characteristics of RC Filter Circuit

When the RC filter circuit is connected, it can prevent the noise on the shunt resistor to make the SC protection

38

malfunction. The RC filter circuit immediately interrupts short-circuit currents due to its characteristics (shown in Figure4-17.) Figure 4-8 and Figure 4-9 show the recommended schemes for the different application of signal input. The RC time constant is determined depending on the applying time of noise interference and the withstand voltage capability of the IGBT.

Figure 4-17. Characteristics of RC Filter Circuit

#### Setting of RC Time Constant

An RC filter (R, C) should be inserted between the current sensing resistor and the IPM CIN pin as shown in Figure 4-15. The RC filter helps prevent erroneous fault detection due to di/dt noise on the shunt resistor and free-wheeling diode recovery current pulses. The RC filter also has the added advantage of producing a time dependent short-circuit trip level that responds quickly to severe low impedance short circuits and slowly to less dangerous overloads conditions. This characteristic is illustrated in Figure 4-17. The RC filter causes a delay in the short-circuit detection that must be coordinated with the short-circuit withstanding capability of the IGBT. For the IPM an RC time constant ( $\tau = R \times C$ ) of 2  $\mu$  s or less is recommended to provide safe operation. A detailed description of the IGBT SOA and short-circuit withstanding capability is given in chapter 5.

Figure 4-11 is a timing diagram showing the operation of the short circuit protection. When current flows in the negative DC bus a voltage is developed across  $R_{SHUNT}$ . The voltage across  $R_{SHUNT}$  is filtered using an RC circuit consisting of R and C and connected to the CIN input on the IPM. If the collector current exceeds the lsc level for long enough to charge the shunt filter capacitor (C) to a voltage greater than Vsc(ref) ( $R_{SHUNT}$ ). The filter (C, R) adds a time delay to prevent erroneous operation of the protection due to free-wheeling diode recovery currents and voltage surges caused by stray inductance in the sensing circuit. Selection of the shunt resistor and filter components will be covered in sections 4.6.4. When the protection is activated all IGBTs are turned off and the open collector fault output is pulled low. The IGBTs remain in the off state and the fault signal remains low for the duration of the fault timer ( $t_{FO}$ ). The length of  $t_{FO}$  is set by the external timing capacitor  $C_{FO}$ . During this time the control input signals are ignored. Normal operation resumes at the first off-to-on transition following the end of the fault timer.

#### 4.6.6 Recommend Wring of Snubber Circuit

Snubber Circuit

In order to prevent ID-IPM from extra surge destruction, the wiring length between the smoothing capacitor and ID-IPM P-N terminals should be as short as possible. Also, a 0.1-0.22  $\mu$ F/630 V snubber capacitor should be mounted in the DC-link close to ID-IPM.

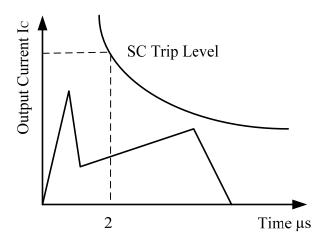

There are three positions (A, B, C) to mount a snubber capacitor as shown in the fig.4-18.

If the snubber capacitor is installed in wrong location 'A' as shown in the Figure, the snubber capacitor cannot suppress the surge voltage effectively.

In order to suppress the surge voltage maximally, the wiring connect to the P port should be as short as possible when mounting a snubber capacitor outside the shunt resistor as shown in position B. If the sunbber capacitor is installed in the position B, that will suppress surge voltage effectively. However, the charging and discharging current generated by the wiring inductance and the snubber capacity will flow though the shunt resistor, which might cause erroneous protection if this current is large enough.

In a word, the "C" position surge suppression effect is greater than the location 'A' or 'B'. The 'B' position is a reasonable compromise with better suppression than in location 'A' without impacting the current sensing signal accuracy. For this reason, the location 'B' is generally used.

Figure 4-18. Recommended snubber circuit location

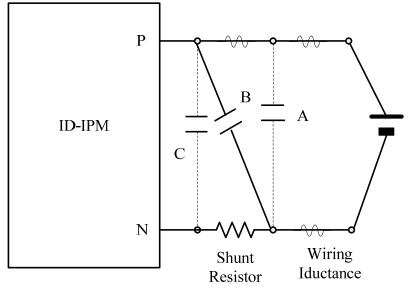

#### • Recommanded Wiring of Shunt Resistor

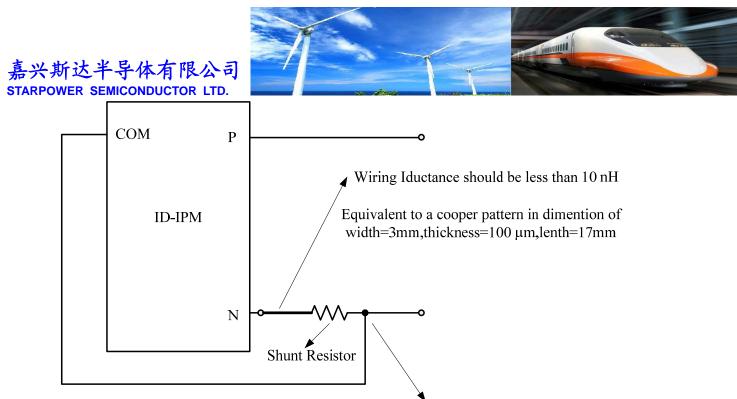

External shunt resistor is employed to detect short-circuit accident. A longer wiring between the shunt resistor and ID IPM might cause so much large surge that might damage built-in IC. To decrease the pattern inductance, the wiring between the shunt and ID IPM should be as short as possible, and using low inductance type resistor instead of long-lead type resistor.

Clothe to the COM terminal as close as possible

Figure 4-19. Recommend Wiring of Shunt Resistor

#### 4.6.7 Parallel Connection

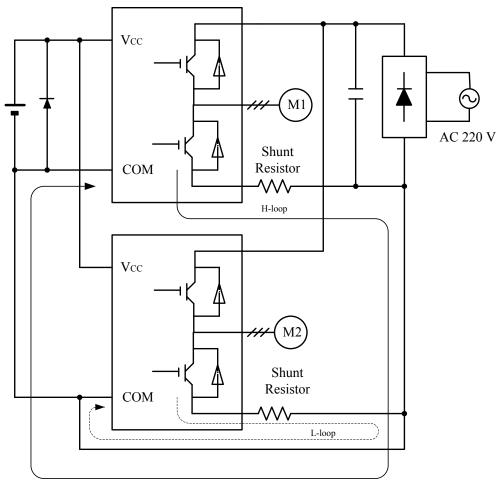

Figure 4-20 shows the circuit of parallel connection of two ID IPMs.

Rout H-loop and L-loop indicate the gate charging path of low-side IGBT in the ID IPM No.2. If the rout is too long, gate voltage might drop due to large voltage drop on the wiring, which will result a bad effect to the second IPM operation (Charging of bootstrap capacitor for high-side is similar, too.).

In addition, noise might easily impose to the wiring impedance. If there are many ID IPM parallel connection. COM pattern becomes long and the influence to other circuit (power supply, protection circuit etc.) by the fluctuation of COM potential is conceivable, therefore parallel connection is not recommended.

Figure 4-20. Parallel Connection

#### 4.6.8 Trouble shooting of IPM

When using the IPM, some simple troubles can be monitor and shooting by table 4-7. By monitoring the  $V_{FO}$  pin signal, we can know when a protection occurs. Due to the build-in under-voltage and over-current protection function, When  $V_{FO}$  pin signal pulls down to ground, we should check which protection triggers.

#### Under-voltage condition:

Check the Vcc whether is lower than 11.5V. By add the decoupling ceramic capacitor close to the Vcc pin could bypass some noise signal.

#### Over-current condition:

Check whether a short circuit or over-current really happens. Some layout may cause the  $C_{SC}$  pin noise to mis-trigger. Approximately a  $0.22 \sim 2 \,\mu$  F by-pass capacitor should be used across each power supply connection terminals.

| Table | 4-7. | Protection   | table |

|-------|------|--------------|-------|

| iabio |      | 1 1010001011 | labio |

| V <sub>CC</sub>    | V <sub>BS</sub>    | V <sub>SC</sub>     | V <sub>FO</sub> |

|--------------------|--------------------|---------------------|-----------------|

| < U <sub>VCC</sub> | Х                  | Х                   | 0               |

| 15V                | < U <sub>VBS</sub> | 0                   | 0               |

| 15V                | 15V                | 0                   | H imp           |

| 15V                | 15V                | > V <sub>trip</sub> | 0               |

Note: A shoot-through prevention logic prevents  $L_{01,2,3}$  and  $H_{01,2,3}$  for each channel from turning on simultaneously. Note:  $U_{VCC}$  is not latched, when  $Vcc > U_{VCC}$ , FO returns to high impedance.

Note: Over-current protection are latched protection and VFO will turn high impedance after the fault condition recovery.

Figure 4-21. Input Filter Function

Note: For high side PWM,  $~~IN_{(XH)}$  pulse width must be  $~\geq~$  1  $\mu$  sec.

Reference impedance for trouble shooting : (For ID20FT06A1S)

Table 4-7. ID IPM Impedance Measurement Range

|     | ID IPM Impedance Measurement Range |                           |  |  |

|-----|------------------------------------|---------------------------|--|--|

| No. | Item                               | Reference impedance (ohm) |  |  |

| 1   | VCC,COM                            | >200M                     |  |  |

| 2   | $IN_{(UH)}, V_{S(U)}$              | 13.0M~15M                 |  |  |

| 3   | $IN_{(VH)}, V_{S(V)}$              | 13.0M~15M                 |  |  |

| 4   | $IN_{(WH)}, V_{S(W)}$              | 13.0M~15M                 |  |  |

| 5   | IN <sub>(UH)</sub> ,COM            | 25K~40K                   |  |  |

| 6   | IN <sub>(VH)</sub> ,COM            | 25K~40K                   |  |  |

| 7   | IN <sub>(WH)</sub> ,COM            | 25K~40K                   |  |  |

| 8   | $V_{B(U)},V_{S(U)}$                | 1.5M~3.0M                 |  |  |

| 9   | $V_{B(V)}, V_{S(V)}$               | 1.5M~3.0M                 |  |  |

| 10  | $V_{B(W)}, V_{S(W)}$               | 1.5M~3.0M                 |  |  |

| 11  | C <sub>SC</sub> ,COM               | 1.0 M ~1.5M               |  |  |

| 12  | C <sub>FOD</sub> ,COM              | 200K~500K                 |  |  |

| 13  | V <sub>FO</sub> ,COM               | 35M~40M                   |  |  |

| 14  | P,N                                | Open                      |  |  |

| 15  | P,U                                | Open                      |  |  |

| 16  | P,V                                | Open                      |  |  |

| 17  | P,W                                | Open                      |  |  |

| 18  | U,N                                | Open                      |  |  |

| 19  | V,N                                | Open                      |  |  |

| 20  | W,N                                | Open                      |  |  |

## Chapter 5 Safe Operating Area

#### 5.1 Safe operating area of the IPM

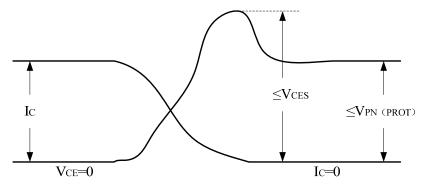

#### 5.1.1 Definition of SOA

By built-in gate drive, under-voltage lockout and short-circuit protection guard them from many of the operating modes that would violate the Safe Operation Area (SOA) of the IGBTs in IPM. A conventional SOA definition that characterizes all possible combinations of voltage, current, and time that would cause power device failure is not required. In order to define the SOA for IPM, the power device capability and control circuit operation must both be considered. The resulting easy to apply switching and short-circuit SOA definitions for the IPM is summarized in this section.

The following describes the SOA (Safety Operating Area) of the IPM.

- V<sub>CES</sub> : Maximum rating of IGBT collector-emitter voltage

- $V_{\text{PN}}~~:~$  Supply voltage applied on P-N terminals

- $V_{\text{PN}}(\text{surge})$ : The add of  $V_{\text{PN}}$  and the surge voltage generated by the wiring inductance and the DC-link capacitor.

$V_{\text{PN(PROT)}}$ : DC-link voltage that IPM can protect itself.

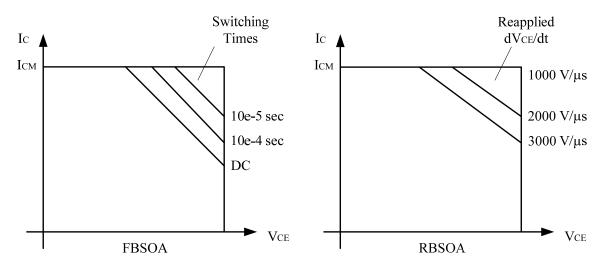

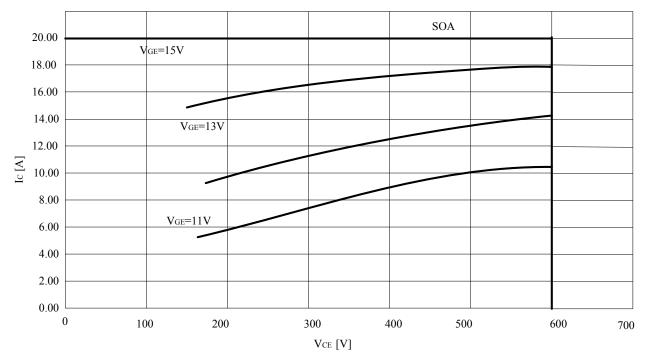

Figure 5-1. SOA for Switching

Figure 5-2. SOA for Short-circuit

#### 5.1.2 Switching Operation

In fact, the V<sub>CES</sub> represents the 600V voltage rating of the IGBTs incorporated into the IPM. But subtracting the surge voltage generated by the stray inductance of the PCB trace and the internal wire bonding of the IPM. Moreover, subtracting from V<sub>PN</sub>(Surge) the surge voltage generated by the stray inductance between the IPM and the DC-link capacitor is V<sub>PN</sub> (Surge), please refer to the data sheet for the rated surge voltage .

- 1. FBSOA Turn on transition (Power dissipation limited)

- 2. RBSOA Turn off transition (Latch-up spec)

Figure 5-3. Safe Operating Area During Switching

Figure 5-4. Safe Operating Area During Short-Circuit (SCSOA)

$V_{CES}$  represents the 600V voltage rating of the IGBTs incorporated into the IPM. Subtracting the surge voltage (100V or less), generated by stray inductance inside the IPM, from  $V_{CES}$  is  $V_{PN}$ (Surge), that is, 500V. Moreover, subtracting from  $V_{PN}$  (Surge) the surge voltage (100V or less) generated by the stray inductance between the IPM and the DC-link capacitor is  $V_{PN(PROT)}$ , that is 400V.

| Items                                                                               | Symbol                  | Condition                                                                                                                  | Rating | Unit |

|-------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|--------|------|

| Supply Voltage                                                                      | V <sub>PN</sub>         | Applied to P-N                                                                                                             | 450    |      |

| Supply Voltage (Surge)                                                              | V <sub>PN (Surge)</sub> | Applied between P-N                                                                                                        | 500    |      |

| Collector - Emitter Voltage                                                         | V <sub>CES</sub>        |                                                                                                                            | 600    |      |

| Self protection Supply<br>Voltage Limit<br>(Short-circuit Protective<br>Capability) | Vpn(prot)               | Applied to DC link, Tj = $125^{\circ}$ C,<br>Vcc = V <sub>BS</sub> = $11.5$ V ~ $20.0$ V,<br>Non-Repetitive, less than 5us | 400    | V    |

Table 5-1. The Absolute Maximum Rating of P-N Voltage

Note: It is recommended that the average junction temperature should be limited to  $Tj \le 150^{\circ}$  C (@ TC  $\le 100^{\circ}$  C) in order to guarantee safe operation.

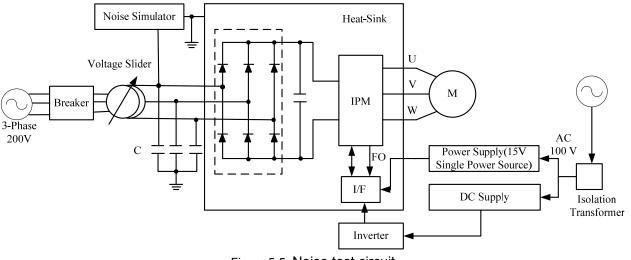

#### 5.2 Noise Immunity Capability

Figure 5-5 shows noise immunity capability testing circuit, ID-IPM have been confirmed to be with  $\pm$ 2KV noise immunity capability, Noise immunity capability extremely depend on the testing system environment, component layout, control substrate patterns, and other factor, so an additional confirmation on prototype is necessary.

47

Figure 5-5. Noise test circuit

#### Note:

C: AC line common-mode filter 4700pF

PWM signals are inputted from microcomputer both directly and through opto-coupler

15V single power-source drive

Test is performed for both IM and DCBLM motors

#### **Test conditions:**

VCC=300V,VD=15V,Ta=25° C, no load.

50ns~1us wide pulses are applied at a random point each 60Hz cycle.

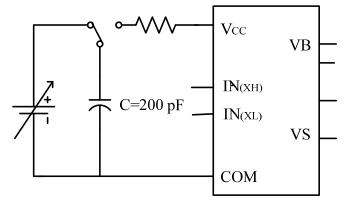

#### 5.3 ESD withstand capability

ID-IPM has been confirmed to be with  $\pm\,$  250V or more withstand capability under the above evaluation circuit.

Figure 5-6. ESD Test Circuit (insides IC)

Qualification Level: Industrial level. MSL3, Lead-free.

ESD Classification:

Human Body Model(HBM): Class2,per JESD22-A114-B

Machine Model(MM): Class B, per EIA/JESD22-A115-A

# Chapter 6 Reference Design

- 6.1 Demo board introduction

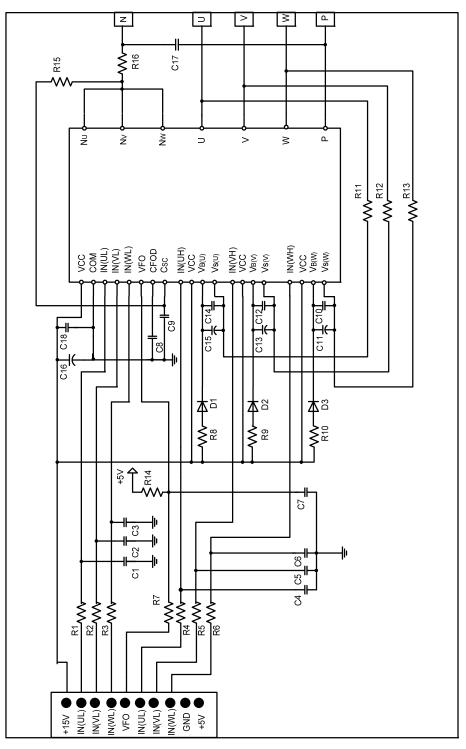

- Demo board schematic

Figure 6-1. Demo Board Schematic

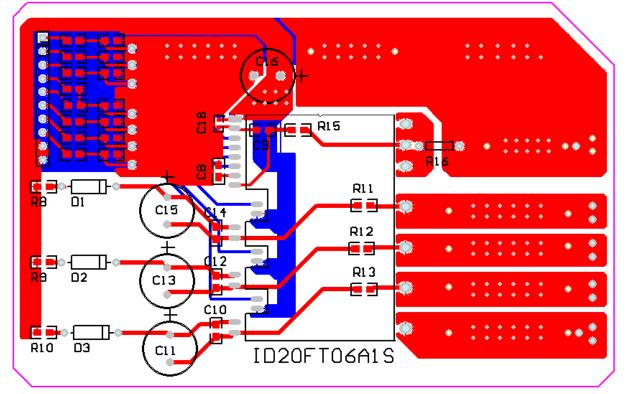

• Demo board layout

Figure 6-2.Demo Board Toplayer

Figure 6-3.Demo Board Bottomlayer

#### • Bill of Materials

Table 6-1.Demo-Board B.O.M List

| Used | Part Type | Rating        | Characteristics        | Definition                                       |

|------|-----------|---------------|------------------------|--------------------------------------------------|

| 1    | C1        | 1 nF          | Ceramic Capacitor      | Low-Side Pull-Down Capacitor                     |

| 2    | C2        | 1 nF          | Ceramic Capacitor      | Low-Side Pull-Down Capacitor                     |

| 3    | C3        | 1 nF          | Ceramic Capacitor      | Low-Side Pull-Down Capacitor                     |

| 4    | C4        | 1 nF          | Ceramic Capacitor      | High-Side Pull-Down Capacitor                    |

| 5    | C5        | 1 nF          | Ceramic Capacitor      | High-Side Pull-Down Capacitor                    |

| 6    | C6        | 1 nF          | Ceramic Capacitor      | High-Side Pull-Down Capacitor                    |

| 7    | C7        | 1 nF          | Ceramic Capacitor      | +5V Bias Voltage Bypass Capacitor                |

| 8    | C8        | 33 nF         | Ceramic Capacitor      | Capacitor for Selection of Fault Out Duration    |

| 9    | C9        | 1 nF          | Ceramic Capacitor      | Bypass Capacitor for Current Sensing             |

| 10   | C10       | 100 nF        | Ceramic Capacitor      | Bypass Capacitor for Bootstrap Supply (Phase U)  |

| 12   | C11       | 6.8 uF 35 V   | Electrolytic Capacitor | Bootstrap Capacitor (Phase U)                    |

| 13   | C12       | 100 nF        | Ceramic Capacitor      | Bypass Capacitor for Bootstrap Supply (Phase V)  |

| 14   | C13       | 6.8 uF 35 V   | Electrolytic Capacitor | Bootstrap capacitor (Phase V)                    |

| 15   | C14       | 100 nF        | Ceramic Capacitor      | Bypass Capacitor for Bootstrap Supply (Phase W)  |

| 16   | C15       | 6.8 uF 35 V   | Electrolytic Capacitor | Bootstrap capacitor (Phase W)                    |

| 17   | C16       | 220 uF 35V    | Electrolytic Capacitor | +15V Bias Voltage Source Capacitor               |

| 18   | C17       | 100 nF 630V   | Film Capacitor         | Snubber Capacitor to Suppress the Spike-Voltage  |

| 19   | C18       | 1uF 35V       | Ceramic Capacitor      | +15V Bias Voltage Bypass Capacitor               |

| 20   | R1        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (UL)        |

| 21   | R2        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (VL)        |

| 22   | R3        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (WL)        |

| 23   | R4        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (UH)        |

| 24   | R5        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (VH)        |

| 25   | R6        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (WH)        |

| 26   | R7        | 100 Ω 1/8 W   | Carbon Film Resistor   | Series Resistor for Signal Interface (Fault-out) |

| 27   | R8        | 20 Ω 1/4 W    | Carbon Film Resistor   | Bootstrap Resistor (Phase U)                     |

| 28   | R9        | 20 Ω 1/4 W    | Carbon Film Resistor   | Bootstrap Resistor (Phase V)                     |

| 29   | R10       | 20 Ω 1/4 W    | Carbon Film Resistor   | Bootstrap Resistor (Phase W)                     |

| 30   | R11       | 5.6Ω 1/4 W    | Carbon Film Resistor   | Emitter Resistor for Switching                   |

| 31   | R12       | 5.6Ω 1/4 W    | Carbon Film Resistor   | Emitter Resistor for Switching                   |

| 32   | R13       | 5.6 Ω 1/4 W   | Carbon Film Resistor   | Emitter Resistor for Switching                   |

| 33   | R14       | 4,7KΩ 1/8 W   | Carbon Film Resistor   | Pull-up Resistor (Fault output)                  |

| 34   | R15       | 1.8 K Ω 1/8 W | Carbon Film Resistor   | Low-pass-Filter for Current Sensing              |

| 35 | R16 | 20m Ω 5 W | Non-inductive Resistor | Shunt Resistor for Current Sensing |

|----|-----|-----------|------------------------|------------------------------------|

| 36 | D1  | 1A 600V   | Fast Recovery Diode    | Bootstrap Diode (Phase U)          |

| 47 | D2  | 1A 600V   | Fast Recovery Diode    | Bootstrap Diode (Phase V)          |

| 48 | D3  | 1A 600V   | Fast Recovery Diode    | Bootstrap Diode (Phase W)          |

嘉兴斯达

#### 6.2 Layout Guide-line

- It is recommended that the wiring of the DC- link power path be as short as possible.

- To suppress surge voltage, a non-inductive snubber capacitor should be mounted as close to P and GND (shunt resistor's return pins) as possible.

- The wiring of N terminal and shunt resistors should be as short as possible and shunt resistors' pin connected DC-link GND also should be as short as possible.

- To prevent the input signals oscillation, an RC coupling at each input is recommended, and the wiring of each input should be as short as possible.

- To minimize the pattern impedance, it is recommended that the bootstrap current path be as short as possible.

- FO output is open collector type. The signal line should be pulled up the positive side of the 5V power supply with approximately 4.7k Ω resistance.

- FO output pulse width should be decided by connecting an external capacitor between CFO and GND terminals.

- Each input signal line should be pulled up to the 5V power supply with approximately 680 Ω ~4.7k Ω resistance.

Approximately a 0.22~2 µ F by-pass capacitor should be used across each power supply connection terminals.

- In order to provide good decoupling between Vcc-GND and V<sub>B</sub>-V<sub>S</sub> terminals, the capacitors shown connected between these terminals should be located very close to the module pins. Additional high frequency capacitors, typically 0.1 μ F, are strongly recommended in order to achieve strong noise immunity.

- High voltage (600V or more) and fast recovery type (less than 100ns) diodes should be used in the bootstrap circuit.

- Each capacitor should be put as nearby the pins of the IPM as possible.

# Chapter 7 Thermal Resistances Concepts Introduction

#### 7.1 Overview

Semiconductor devices are very sensitive to junction temperature, i.e., as the junction temperature increases, the operating characteristics of a device are altered from normal, and the failure rate increases exponentially. This makes the thermal design of the package a very important factor in the device development stage, and also in an application field.

To gain insight into the device's thermal performance, it is normal to introduce thermal resistance. The thermal resistance is a measure of the temperature change across a package caused by power dissipation of the packaged semiconductor device. It is an indication of the heat transfer from the semiconductor device through the package materials out to the environment in terms of temperature per unit of power. Thermal resistance data can be used by the de-signer or customer to estimate the junction temperature of their die in operation.

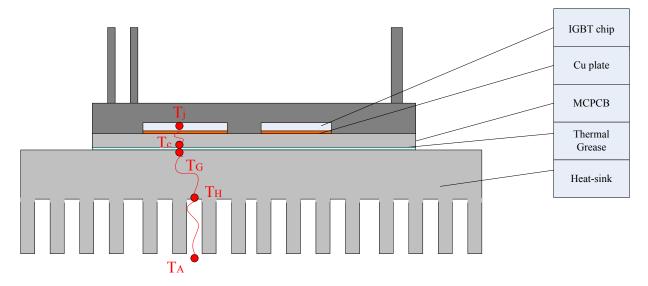

Figure 7-1 shows a thermal network of heat flow from junction-to-ambient for the SDIP-IPM including a heat sink.

The thermal resistance of the ID-IPM is defined in the following equation.

The thermal resistance of a semiconductor device is generally as:

$$R_{\theta JX} = \frac{T_J - T_X}{P_H} \tag{7-1}$$

Where  $R_{\theta JX}$  = Thermal resistance from device junction to the specific environment (alternative symbol is  $\theta_{JX}$ ) [°C/W]

$T_J$  = device junction temperature in the steady state test condition [°C]

$T_X$  = reference temperature for the specific environment [°C]

$P_H$  = power dissipated in the device [W]

The selection of a reference point is arbitrary, but usually the hottest spot on the back of a device on which heat sink is attached is chosen. This is called junction-to-case thermal resistance,  $R_{\partial JC}$ .

$$R_{\theta JC} = \frac{T_J - T_C}{P_H}$$

(7-2)

Where  $T_{C}$  = device case temperature in the steady state test condition [°C]

When the reference point is an ambient temperature, this is called junction-to-ambient thermal resistance,  $R_{BJA}$ .

$$R_{\theta JA} = \frac{T_J - T_A}{P_H} \tag{7-3}$$

Where  $T_A$  = Ambient temperature [°C]

$R_{\theta JA}$  (°C/W) indicates the total thermal performance of the SDIP-IPM including the heat sink. Basically  $R_{\theta JA}$  is a serial summation of various thermal resistances,  $R_{\theta JC}$ ,  $R_{\theta CG}$ ,  $R_{\theta CH}$  and  $R_{\theta HA}$ .

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CG} + R_{\theta GH} + R_{\theta HA}$$

(7-4)

Where,  $R_{\theta CG}$  is contact thermal resistance due to the thermal grease between the package and the heat sink, and  $R_{\theta CH}$  is heat sink thermal resistance, respectively. From the equation (7-4), it is clear that minimizing  $R_{\theta CH}$  and  $R_{\theta HA}$  is an essential application factor to maximize the power carrying ability of the device as well as the minimizing of  $R_{\theta IC}$  itself. Usually the value of  $R_{\theta CH}$  is proportional to the thermal grease and governed by the skill at the assembly site, while  $R_{\theta HA}$  can be handled to some extent by selecting an appropriate heat sink.

Fig. 7-1 Thermal Network of the ID-IPM from Junction to Ambient

#### 7.2 Measurement Method

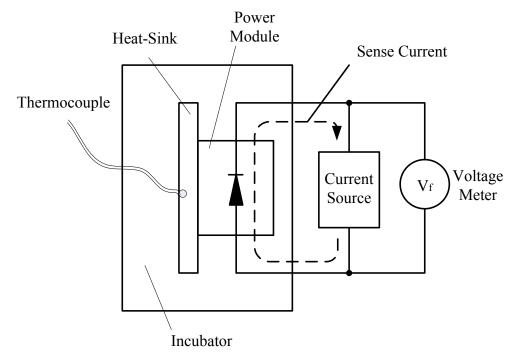

During the thermal resistance test, some constants in equation (7-2), i.e.,  $T_c$ ,  $T_A$ , and P can be measured directly. The only unknown parameter is the junction temperature,  $T_J$ . The Electrical Test Method (ETM) is a popular technique for measuring the junction temperatures in electronic components. However, without a well-defined standard methodology for making thermal measurement, it has become increasingly difficult to accurately determine junction temperature under actual operating and environmental conditions. Knowing the semiconductor device thermal resistance for a specific electronic package allows both the manufacturer and user to determine the junction temperature of the device.

Accurate and correct thermal measurements are difficult to make because of the many variables that impact the final results. Electrical considerations (such as power, voltage and current levels, input and output levels, etc.), environmental considerations (mounting configuration, surroundings, mounting methodology, etc.) and selection of the junction temperature sensor will directly affect the thermal measurement.

55

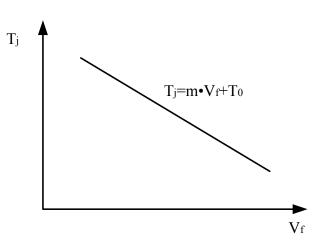

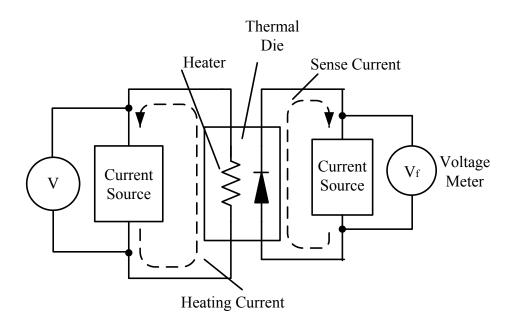

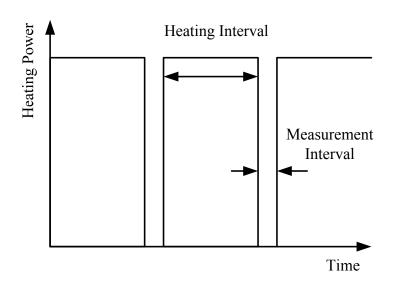

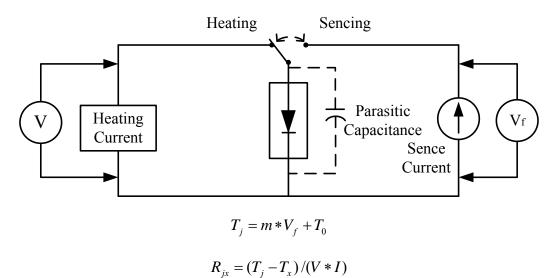

The Electrical Test Method (ETM) uses the forward voltage dropped of a junction as the temperature sensitive parameter and is variously known as the "diode-forward-drop" method from original applications with power diodes and bipolar power transistors. It is based on a temperature and voltage dependency exhibited by all semiconductor diode junctions. This relationship can be measured and used to compute the semiconductor junction temperatures in response to power dissipation in the junction region. The voltage-temperature relationships are an intrinsic electro-thermal property of semiconductor junctions, and are characterized by a nearly linear relationship between forward-biased voltage drop and junction temperature when a constant forward-biased current is applied. This constant current is called the "sense current" (also "measurement current"). This voltage drop of the junction is called Temperature sensitive Parameter (TSP). Figure 7-2 illustrates the concept of measuring this voltage versus junction temperatures.

Fig. 7-2 Illustrations of the Bath Method for TSP Measurement

When the DUT attains thermal equilibrium with the hot fluid, a sense current is applied to the junction. Then the voltage drop across the junction is measured as a function of the junction temperatures. The measurement current through the temperature sensing diode must be large enough to obtain a reliable forward voltage reading not influenced by surface leakage effects but small enough not to cause significant self heating. For instance, 1mA, 10mA depending on the device type. The measurements are repeated over a specific temperature range with some specified temperature steps. Figure 7-3 shows a graph of typical result.

Figure 7-3. Typical Example of a TSP Plot with Constant Sense Current

The relationship between the junction temperature and voltage drop can be expressed mathematically as in the calibrating relationship,

$$T_J = m * V_f + T_0 \tag{7-5}$$